Rubriques tendance

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Je me suis un peu perdu dans tous les acronymes et le jargon ici, alors j'ai demandé à Claude de l'expliquer sans utiliser d'acronymes et maintenant tout a parfaitement du sens (tldr; bande passante ⟹ simplicité) :

C'est une discussion technique fascinante sur l'entraînement de grands modèles de langage à grande échelle.

La Conversation Principale

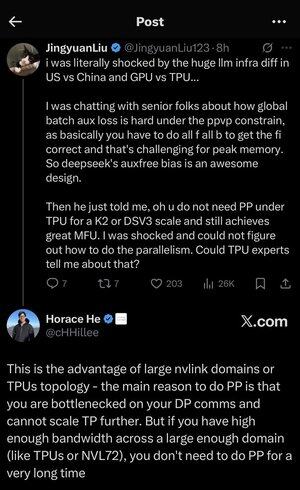

Jingyuan Liu exprime sa surprise de découvrir qu'il n'est pas nécessaire d'utiliser certaines techniques d'optimisation complexes lors de l'utilisation de TPUs (Tensor Processing Units - les puces AI spécialisées de Google) par rapport aux GPUs (Graphics Processing Units - généralement les puces de NVIDIA).

Concepts Techniques Clés Expliqués :

Types de Matériel :

•GPU (Graphics Processing Unit) : À l'origine conçu pour les graphiques, maintenant largement utilisé pour l'IA. NVIDIA domine ce marché.

•TPU (Tensor Processing Unit) : Puces conçues sur mesure par Google spécifiquement pour l'apprentissage automatique.

Stratégies de Parallélisme :

Lors de l'entraînement de modèles d'IA massifs, vous devez répartir le travail sur de nombreuses puces. Il existe plusieurs façons de le faire :

1) Parallélisme de Données (DP) : Chaque puce traite différents lots de données avec la même copie du modèle.

2) Parallélisme de Tenseur (TP) : Les opérations mathématiques du modèle sont réparties sur les puces.

3) Parallélisme de Pipeline (PP) : Différentes couches du modèle sont placées sur différentes puces, créant un pipeline.

Le Défi Technique Discuté :

Le problème de la perte auxiliaire : Lors de l'entraînement de modèles très grands, vous ajoutez souvent des "pertes auxiliaires" (objectifs d'entraînement supplémentaires) à des couches intermédiaires pour aider les gradients à mieux circuler dans le réseau. Sous les contraintes de PPVP (Parallélisme de Pipeline avec Partitionnement Variable), cela devient complexe car :

•Vous devez faire "tous f tous b" (tous les passages avant, puis tous les passages arrière)

•C'est un défi pour l'utilisation de la mémoire maximale car vous devez stocker les résultats intermédiaires.

L'innovation de DeepSeek : Ils ont développé un design "auxfree bias" qui apparemment évite d'avoir besoin de ces pertes auxiliaires tout en s'entraînant efficacement.

La Révélation Surprenante :

L'expert senior a dit à Jingyuan qu'avec des TPUs à l'échelle K2 ou DSV3 (ce sont des configurations de cluster avec des centaines ou des milliers de puces), vous pouvez atteindre une excellente MFU (Utilisation des FLOPs du Modèle - essentiellement à quel point vous utilisez efficacement le matériel) SANS utiliser le Parallélisme de Pipeline.

Pourquoi est-ce surprenant ?

•Le Parallélisme de Pipeline est généralement considéré comme essentiel pour l'entraînement à grande échelle.

•C'est une technique complexe qui nécessite une optimisation minutieuse.

•Être capable de l'éviter simplifie tout de manière significative.

L'Explication de Horace He :

Il explique POURQUOI cela est possible avec les TPUs :

L'avantage de la bande passante : Les TPUs et les clusters NVIDIA haut de gamme (comme NVL72 - la dernière configuration de 72 GPU de NVIDIA avec des interconnexions NVLink) ont une bande passante si élevée entre les puces qu'ils peuvent gérer les exigences de communication sans Parallélisme de Pipeline.

L'idée clé :

•Le Parallélisme de Pipeline est principalement nécessaire lorsque vous êtes "bottlenecked on DP comms" (limité par la rapidité de communication pendant l'entraînement parallèle de données).

•Si vous avez suffisamment de bande passante sur un domaine suffisamment large (cluster interconnecté), vous pouvez simplement utiliser des stratégies de parallélisme plus simples.

•Cela fonctionne "pendant très longtemps" - ce qui signifie que vous pouvez entraîner même des modèles très grands sans atteindre les limites.

L'Intuition :

Pensez-y comme à un système autoroutier :

•Les clusters GPU traditionnels sont comme avoir des routes étroites entre les villes, donc vous avez besoin d'un routage complexe (Parallélisme de Pipeline) pour éviter les embouteillages.

•Les clusters TPU ou les GPU connectés par NVLink sont comme avoir d'énormes autoroutes - vous pouvez simplement envoyer tout directement sans routage sophistiqué.

C'est un gros problème car le Parallélisme de Pipeline est complexe à mettre en œuvre, à déboguer et à optimiser. Être capable de l'éviter tout en atteignant une haute efficacité rend l'ensemble du processus d'entraînement beaucoup plus simple et plus fiable.

La discussion met en lumière comment les avancées dans la technologie d'interconnexion matérielle (les "routes" entre les puces) peuvent fondamentalement changer les stratégies logicielles nécessaires pour un entraînement efficace de l'IA.

16,72K

Meilleurs

Classement

Favoris